# EMBEDDED SYSTEMS January 2014 Volume 10 | Number 1 MIL-EMBEDDED.COM

John McHalo

Radar market

Special Report Maritime radar

#### Mil Tech Trends

High-performance SRAMs for DSP applications

## Industry Spotliaht

FPGA boards for military signal processing

EMBEDDED SIGNAL PROCESSING ENABLES ADVANCED RADARS WITH LOW LATENCY

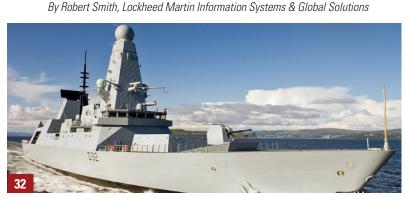

ISR as a Service: Providing users with affordable surveillance and reconnaissance – By Robert Smith, Lockheed Martin

CAR\_26

Fusing sensor data for radar displays

P 32

\_Alar Compound

XUNKNOWN 35

UNKNOWN\_44ATI:LandTrack

# Module and System-Level Solutions from X-ES

XPedite7570 4th Gen Intel® Core™ i7-based 3U VPX SBC with XMC/PMC

XCalibur1840 Freescale QorlQ T4240-based 6U VPX SBC with dual XMC/PMC

XPedite2400 Xilinx Virtex-7 FPGA-based XMC with high-throughput DAC

# Secure Ethernet Switches and IP Routers

XPedite5205 Secure Gigabit Ethernet router XMC utilizing Cisco™ IOS®

XChange3018 3U VPX 10 Gigabit Ethernet managed switch and router

# **High-Capacity Power Supplies**

XPm2220 3U VPX 300W power supply with EMI filtering for MIL-STD-704 & 1275

# Rugged, SWaP-Optimized, COTS-Based Systems

XPand4200 Sub-1/2 ATR, 6x 3U VPX slot system with removable SSDs

XPand6200 SFF 2x 3U VPX system with removable SSD and integrated power supply

XPand6000 SFF Intel® Core™ i7 or Freescale QorlQ-based system with XMC/PMC

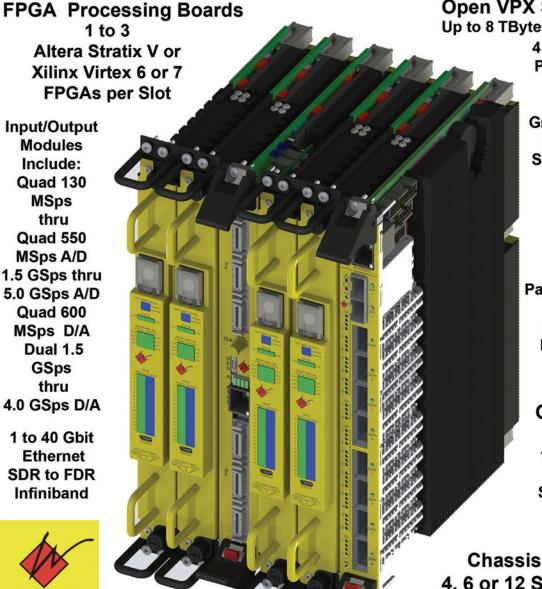

# Annapolis Micro Systems

The FPGA Systems Performance Leader

# WILDSTAR OpenVPX Ecosystem

**Quad 130 MSps** thru **Quad 550** MSps A/D 1.5 GSps thru 5.0 GSps A/D **Quad 600** MSps D/A **Dual 1.5 GSps** thru 4.0 GSps D/A

1 to 40 Gbit Ethernet SDR to FDR Infiniband

**Open VPX Storage** Up to 8 TBytes Per Slot

4 - 8 GBytes Per Second

GEOINT. **Ground Stations.** SDR, Radar, Sigint, COMINT, ELINT, DSP, Network Analysis, Encryption, **Image** Processing, Pattern Matching. Oil & Gas Exploration, Financial and Genomic Algorithms,

**Open VPX** Switch 1 to 40 Gbit **Ethernet** SDR to FDR Infiniband

4, 6 or 12 Slot Up to 14G

# **High Performance Signal and Data Processing** in Scalable COTS FPGA Computing Fabric

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com USA (410) 841-2514 www.annapmicro.com

# www.mil-embedded.com Wilitar EMBEDDED SYSTEMS

#### ON THE COVER:

Top photo: Raytheon's Patriot Air and Missile Defense System's radar for Taiwan and Saudi Arabia upgraded from a VME technology to a OpenVPX-based system from Mercury Systems. Photo courtesy

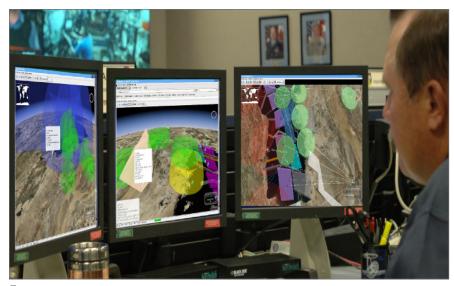

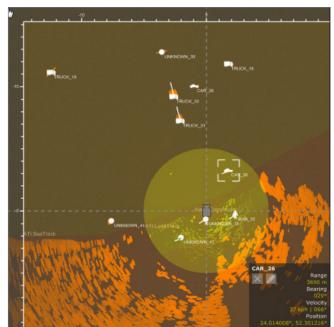

Bottom photo: This photo shows track data and radar video from two sensors. Photo courtesy of Cambridge Pixel.

2014 Januar

Volume

# COLUMNS

#### **Editor's Perspective**

Radar market promising for embedded computing designers By John McHale

# Field Intelligence

Budget cuts spur use of rugged COTS systems By Charlotte Adams

#### Mil Tech Insider

Latest 40 Gbps SBCs drive new class of HPEC-Lite systems for ISR applications By Alan Baldus

# **DEPARTMENTS**

10 **Defense Tech Wire** By Amanda Harvey

#### E-CASTS

http://ecast.opensystemsmedia.com

# Innovation in radar and electronic warfare systems through signal processing

Presented by GE Intelligent Platforms, Pentek, Mercury Systems, Thermacore http://ecast.opensystemsmedia.com/445

# Maximizing system performance in time and space partitioned DO-178-certifiable safety-critical systems

Speaker: Tim King, DDC-I http://ecast.opensystemsmedia.com/447

# WEB RESOURCES

Subscribe to the magazine or E-letter Live industry news | Submit new products http://submit.opensystemsmedia.com

White papers:

Read: http://whitepapers.opensystemsmedia.com Submit: http://submit.opensystemsmedia.com

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2014 OpenSystems Media © 2014 Military Embedded Systems ISSN: Print 1557-3222

# MIL TECH TRENDS | Signal processing trends in radar, sonar, and electronic warfare

- 20 Embedded signal processing enables advanced radars and EW systems with low latency By John McHale

- 24 Using high-performance SRAMs to increase performance in DSP-intensive applications By Suhail Zain, Cypress Semiconductor

- 28 Common EW and radar systems for emerging military missions By A. Lorne Graves, Mercury Systems

- 32 Fusing video and radar tracks in multisensor military security By Dr. David G. Johnson, Cambridge Pixel

# **INDUSTRY SPOTLIGHT** | FPGAs for radar and electronic warfare systems

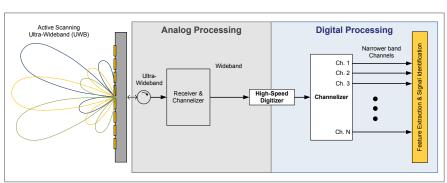

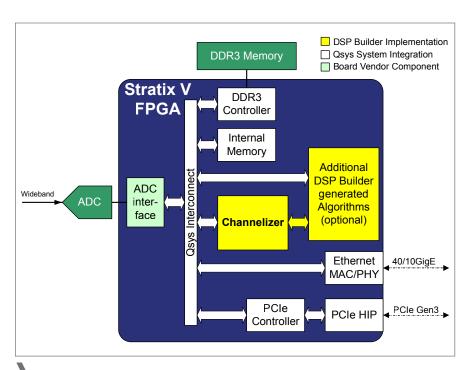

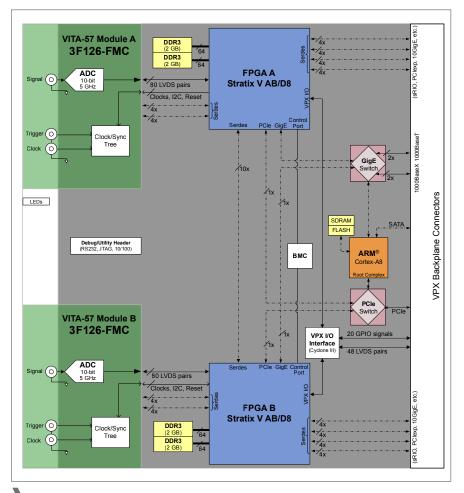

- Digital channelizer implemented on COTS FPGA board: 36 A flexible solution for military signal processing By Jeff Milrod, BittWare

- 40 Designing a general-purpose FPGA DSP card for EW, radar applications using the latest generation of FPGAs By Denis Smetana, Curtiss-Wright

Whether you're radar manufacturer or systems integrator, Cambridge Pixel's hardware-agnostic open-systems approach puts you in control offering freedom, flexibility, reduced through life costs and ease of technology refresh.

#### Simulation with ASTERIX tracks and video

Our newly announced SPx Simulator with optional HPx-300 Radar Output hardware supports the development of complex multi-radar, multi-target scenarios to generate representative primary radar, AIS, NMEA, navigation, ASTERIX CAT-48, CAT-34 and CAT-240 messages.

# **Radar Toolkit**

The Cambridge Pixel family of radar components covers scan conversion, network streaming, target tracking and recording. We offer modular toolkits for developers and we provide cost-effective ready-to-run applications for PC-based radar display and tracking under Windows and Linux.

## The Cambridge Pixel Approach

Our approach is to provide flexible, easy-to-use modules of software. We can supply complete turn-key solutions or individual software modules for inclusion in a customer's existing application. And it is all backed by Cambridge Pixel's do-what-it-takes technical support to help you when you need it.

**Tech Source**

Cambridge Pixel Ltd

New Cambridge House

Litlington Royston

Herts SG8 0SS UK

T: +44 1763 852749

enquiries@cambridgepixel.com

www.cambridgepixel.com

442 Northlake Blvd,

Altamonte Springs,

FL 32701, USA

T: 407-262-7100

embeddedgraphics@techsource.com

www.techsource.com

# **New HPx-300 Radar Output**

The new HPx-300 Radar Output Card generates radar video signals for system testing, simulation, training and video streaming

- Highly configurable output signals

- Output timing synchronised to input data

- Video (x2), Trigger, ACP/ARP, SHM, parallel azimuth

- Configurable scan rates, PRFs

- Compact half length PCle card

- Available with SPx Simulator and Development software

#### ADVERTISER INFORMATION

| ١L | OVER | TISER INFORMATION                                                                                                      |

|----|------|------------------------------------------------------------------------------------------------------------------------|

|    | Page | Advertiser/Ad Title                                                                                                    |

|    | 14   | ACCES I/O Products, Inc. – USB embedded I/O solutions – Rugged, industrial strength USB                                |

|    | 42   | AIM-USA – What's in the box?                                                                                           |

|    | 3    | Annapolis Micro Systems, Inc. –<br>WILDSTAR OpenVPX ecosystem                                                          |

|    | 45   | Annapolis Micro Systems, Inc. –<br>COTS WILD OpenVPX ecosystem                                                         |

|    | 45   | Annapolis Micro Systems, Inc. –<br>WILDSTAR FPGA COTS processing boards                                                |

|    | 45   | Annapolis Micro Systems, Inc. –<br>COTS WILD data storage solution                                                     |

|    | 23   | Avionics Interface Technologies –<br>Test instrumentation                                                              |

|    | 5    | <b>Cambridge Pixel</b> – Primary radar is our passion                                                                  |

|    | 21   | Data Device Corporation –<br>Enabling more                                                                             |

|    | 43   | Diamond Systems Corporation –<br>Rugged Gigabit Ethernet switches                                                      |

|    | 30   | Elma Electronic — SigPro1:<br>Signal acquisition, FPGA-based record/<br>playback system                                |

|    | 46   | Embedded World – Summit for innovations                                                                                |

|    | 39   | Evans Capacitor Company –<br>Evanscaps everywhere                                                                      |

|    | 19   | Excalibur Systems, Inc. – Dragon – it's not a myth                                                                     |

|    | 47   | <b>GE Intelligent Platforms, Inc.</b> –<br>High-performance RADAR with out-of-box<br>readiness                         |

|    | 37   | Interface Concept – SBCs premium<br>Intel and Freescale processors                                                     |

|    | 44   | Kimdu Corporation – Protocol converters                                                                                |

|    | 27   | LCR Embedded Systems –<br>Rugged systems engineered for your<br>application                                            |

|    | 35   | Mercury Systems – Innovation that detects                                                                              |

|    | 48   | <b>Pentek, Inc.</b> – Got tough software radio design challenges?                                                      |

|    | 34   | Phoenix International – Rugged deployable RAID data storage                                                            |

|    | 31   | <b>Proto Labs</b> – Others say they're FAST but do they have the scale to deliver?                                     |

|    | 44   | Rakon – Rakon's digital pulse compression sub-systems                                                                  |

|    | 15   | SynQor – Uninterruptible power supply                                                                                  |

|    | 44   | Thermacore International, Inc. –<br>Thermacore delivers thermal performance<br>advantages in the world's hottest spots |

|    | 44   | Wind River Aerospace & Defense Division – Safety-critical market leader                                                |

|    | 2    | X-ES – Module and system-level solutions from X-ES                                                                     |

|    | 44   | X-ES – XPedite2470 – Virtex-7 FPGA-based<br>3U OpenVPX module                                                          |

|    | 44   | X-ES – XPand6208 – High-performance                                                                                    |

# Military EMBEDDED SYSTEMS

#### MES Editorial/Production Staff

John McHale, Editorial Director jmchale@opensystemsmedia.com

Lisa Daigle, Assistant Managing Editor Idaigle@opensystemsmedia.com

Amanda Harvey, Assistant Editor aharvey@opensystemsmedia.com

Steph Sweet, Creative Director ssweet@opensystemsmedia.com

# Sales Group

Tom Varcie, Senior Account Manager tvarcie@opensystemsmedia.com

Rebecca Barker, Strategic Account Manager rbarker@opensystemsmedia.com

Eric Henry, Strategic Account Manager ehenry@opensystemsmedia.com

Ann Jesse, Strategic Account Manager ajesse@opensystemsmedia.com

Susan MacLeod, Strategic Account Manager smacleod@open system smedia.com

Kathleen Wackowski, Strategic Account Manager kwackowski@opensystemsmedia.com

Christine Long Vice President, Online Business clong@opensystemsmedia.com

#### Asia-Pacific Sales

Elvi Lee, Account Manager elvi@aceforum.com.tw

#### **Regional Sales Managers**

Barbara Quinlan Southwest bquinlan@opensystemsmedia.com

Denis Seger Southern California dseger@opensystemsmedia.com

Sydele Starr Northern California sstarr@opensystemsmedia.com

# Reprints and PDFs

republish@opensystemsmedia.com

# OpenSystems Media Editorial/Production Staff

John McHale

**Editorial Director**

VITA Technologies

VITA Technologies

Military Embedded Systems

Military Embedded Systems

Military Embedded Systems

Military Embedded Systems

scole@opensystemsmedia.com

Jerry Gipper, Editorial Director

jgipper@opensystemsmedia.com

PICMG Systems & Technology

Curt Schwaderer, Technology Editor **Embedded Computing Design**

cschwaderer@opensystemsmedia.com

Sally Cole, Senior Editor

Amanda Harvey, Assistant Editor

Lisa Daigle, Assistant Managing Editor

# Embedded Committee Military DSP-FPGA.com MDUSTRIAL PC2024 form factors PICMG VITATECHNOLOGIES

Joe Pavlat, Editorial Director PICMG Systems & Technology jpavlat@opensystemsmedia.com

Monique DeVoe Assistant Managing Editor **Embedded Computing Design**

DSP-FPGA.com

mdevoe@opensystemsmedia.com

Brandon Lewis, Associate Editor PICMG Systems & Technology PC/104 and Small Form Factors Industrial Embedded Systems blewis@opensystemsmedia.com Konrad Witte, Senior Web Developer

Steph Sweet, Creative Director

David Diomede, Creative Services Director

Joann Toth, Senior Designer

## Corporate

Patrick Hopper, Publisher phopper@opensystemsmedia.com

Karen Layman, Business Manager

30233 Jefferson

St. Clair Shores, MI 48082 Tel: 586-415-6500

www.opensystemsmedia.com

Rosemary Kristoff, President rkristoff@opensystemsmedia.com

Wayne Kristoff, CTO

Emily Verhoeks, Financial Assistant

16626 E. Avenue of the Fountains, Ste. 201 Fountain Hills, AZ 85268

Tel: 480-967-5581

## Subscriptions

Tel: 586-415-6500

# www.opensystemsmedia.com/subscriptions

subscriptions@opensystemsmedia.com

small form factor system

# Radar market promising for embedded computing designers

By John McHale, Editorial Director

Welcome to our 2014 Radar Issue. Why have an issue focused on radar? Simple: the radar market, along with Electronic Warfare (EW), shows the most promise for embedded-computing system designs.

As Brad Curran, an analyst with Frost & Sullivan says, "Radar is hot. In 2011 there were 79 radar contracts totaling \$3.27 billion with Raytheon as the leading producer. In 2012 the total contracts increased to 88, worth \$4.26 billion, with Raytheon

again as the leader. In 2013 there were 79 radar contracts totaling \$4.03 billion, with Raytheon leading again with 24 of the contracts for \$2.09 billion."

Raytheon's reign at the top of the radar world looks to continue for a while, especially with their win of the U.S. Navy's Air and Missile Defense Radar (AMDR) contract - a next-generation defensive system for Arleigh Burke-class destroyers. The new radar will enhance ships' ability to detect ballistic missiles, as well as air and surface targets, according to Raytheon. The AMDR will be scalable, working with any ship or mission. It will

make use of digital beamforming to provide wide-area surveillance while gaining high precision with multiple, simultaneous radar beams. It will also have a radar resource scheduler to allow it to perform multiple missions simultaneously without extending the demand on the ship's prime power system. It is based on other Raytheon active phased-array radars, which make use of sometimes thousands of individual transmitters on each radar face to steer signals electronically, according to a Raytheon release.

Maritime radar is also a growth market, Curran says. "For 2013 there were 41 contracts for \$1.59 billion, with Raytheon leading. This trend will continue as ballistic-missile defense upgrades for Aegis ships and anti-ship missile defenses are a priority, along with airborne maritime surveillance as the P-8, Triton Dome, and other Unmanned Aerial Vehicles (UAVs) are deployed." For more on maritime radar and Raytheon, see Senior Editor Sally Cole's Special Report on page 12.

The market has a mix of new radar designs and upgrades of signal-processing systems. "Radar retrofits typically involve a switch from VME to VPX systems in a shelf upgrade," says Bill Pilaud, Continuum HPEC Manager for Curtiss-Wright Controls Defense Solutions in Ashburn, VA. "VPX provides such a large improvement in threat-detection capability that it is hard to resist if you have the funding."

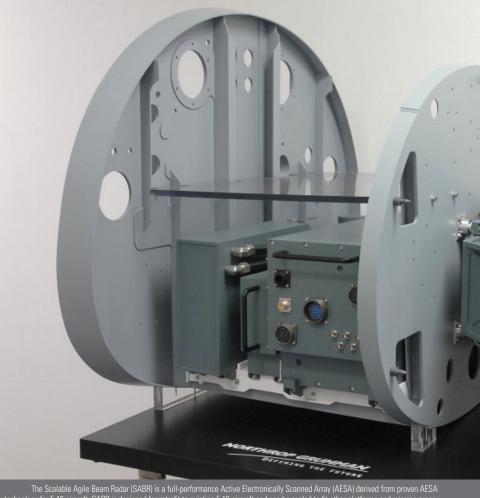

New designs include programs such as the Air Force Dismount Detection Radar, says Dr. Paul Monticiollo, CTO at Mercury Systems in Chelmsford, MA. "We are also seeing radar and EW systems being moved onto UAV platforms. The F-16 and F-15E radar-modernization programs, where mechanically scanned arrays are being replaced by Active Electronically Scanned Arrays (AESAs). Enhancing the downstream signal processing is also a big part of these tech refreshes."

"Pretty much every company presenting or attending the Embedded Tech Trends conference in Phoenix in January 2014 listed radar as the key area for their signal-processing solutions."

Examples of programs that upgraded their radar signal-processing systems with Commercial-Off-The-Shelf (COTS) include the Raytheon Patriot Missile System radar and the Lockheed Martin AN/TPQ-53 (Q-53) counterfire target-acquisition radar. Designers of these systems like the high speeds of multicore processors such as the 4th-generation Intel Core i7 – also known as Haswell - high-performance FPGAs from Xilinx and Altera. For more on signal-processing trends, see my article in the Mil Tech Trends section on page 20.

"A lot of our radar business consists of upgrades to systems that are 15 or 20 years old," says Rodger Hosking, Vice President and cofounder of Pentek in Upper Saddle River, N.J. "Not only do our customers get improved performance with these upgrades, but they also see tremendous savings in total life-cycle costs because maintenance costs on older radar systems can be quite high."

Pretty much every company presenting or attending the Embedded Tech Trends conference (www.embeddedtechtrends.com) in Phoenix in January 2014 listed radar as the key area for their signal-processing solutions. In addition to the companies mentioned above, they include Kontron, 4DSP LLC, Vadatech, Elma, Alpha Data, CES, Artysen Embedded Technologies (formerly Emerson Network Power), AcQ, ADLINK, and Interface Concept.

We've also packed the issue with contributed articles from embedded computing companies, along with an article from Lockheed Martin on ISR as a Service on page 16. Our Mil Tech Trends section includes a piece from Cambridge Pixel on radardisplay processing, another from Cypress Semiconductor on using high-performance SRAMs for signal processing, and one from Mercury Systems on signal processing for EW. In our Industry Spotlight section, Bittware and Curtiss-Wright Controls Defense Solutions penned articles on FPGA technology for use in radar and EW systems.

# **Budget cuts spur use of rugged COTS** systems

By Charlotte Adams

COTS is attractive at the subsystem level because it can reduce risk levels of a program - especially cost and time to market - since there is no upfront Non-Recurring Engineering (NRE) overhead. Delivery time can be a matter of weeks and, because it is already ruggedized, the function takes less time to field. The subsystem, already packaged in a standard chassis, could serve as a platform for software development, interoperate as part of a larger system, or plug into a smaller platform at the system level after appropriate testing and certifications have been completed. Rugged COTS subsystems or systems typically have been tested in a laboratory, simulating the intended operating environment, and have achieved a correspondingly high Technology Readiness Level (TRL).

COTS technology can also reduce technical risks, from the early integration of cards, to analysis and testing of how well they work together, to interoperability with other systems, through operation and lifecycle support. Much work has been done upfront to ensure hardware compatibility and to fine-tune the operation of low-level software such as board support packages, drivers, and operating systems.

Ruggedness is also important. Although there is no overarching standard for this quality, vendors typically offer several

Figure 1 | The GE Intelligent Platforms D8I-3VF1 is a 3U VPX, forced air-cooled platform.

levels of ruggedization - based on military specs - relating to prospective environmental factors such as temperature, shock, vibration, sand, dust, humidity, and saltwater corrosion. Products are often tested to procedures found in MIL-STD-810.

Ruggedization is now so common in military and aerospace products that it's typically considered from the beginning – from design, assembly, and test on through thermal management, mechanical engineering, and hermetic control. Ruggedization techniques include elements such as parts screening, substrate material selection, conformal coatings, stiffening, and cooling.

A rugged COTS system can offer a range of processing functions, such as generic CPU boards, video processing, and special-purpose signal processing cards with hundreds of processing engines per chip. But COTS also needs to be flexible, especially at the system level, where so many elements are provided that customers could literally be boxed in before they know it. It's important for the vendors to have built into their menu of architectures a wide range of flexibility, especially as to the I/O configuration.

An example of a rugged COTS subsystem appropriate for HPEC applications such as radar is the GE Intelligent Platforms D8I-3VF1, a 3U VPX, forced air-cooled platform with as many as three Intel multicore Core i7 boards expandable to eight slots, including video capture, General Purpose Graphics Processing Unit

(GPGPU) and switch cards (see Figure 1). Its I/O capability ranges from MIL-STD-1553 and Gigabit Ethernet (GbE).

#### Increased demand

Rugged COTS subsystems and systems are becoming more common because the demand is growing. For example, U.S. Department of Defense (DoD) spending for COTS-equipped aircraft, such as the P-8 Sub Hunter and the KC-46 Tanker, reached \$4.71 billion in 2012 and will spike between 2013 and 2016, as these programs reach full production, according to Frost & Sullivan, a U.S. market analysis firm.

Revenues for unmanned systems - which leverage rugged COTS technology and put a premium on ruggedization, as well as economies of Size, Weight, and Power (SWaP) - are expected to grow even faster. The aviation side of this market could grow at an annual 12 percent compound annual growth rate, hitting \$18.7 billion in 2018, say analysts at Market Research Media. That could produce \$86.5 billion in revenues from 2013 to 2018. These numbers don't include the proliferation of civilian Unmanned Aerial Vehicles (UAVs), which recently received the blessing of the U.S. Congress. Civilian UAVs will also be deployed with COTS systems.

The military clearly wants more economical and less time-consuming solutions, and rugged COTS is a proven approach to this end.

defense.ge-ip.com

# Latest 40 Gbps SBCs drive new class of HPEC-Lite systems for ISR applications

By Alan Baldus An industry perspective from Curtiss-Wright Controls Defense Solutions

The embedded defense and aerospace industry has recently seen the emergence of new embedded system elements that support 40 Gbps fabrics. These higher bandwidth hardware solutions include Single Board Computers (SBCs), DSP engines, GPGPUs, FPGA engines, network switches, and Gen3 OpenVPX backplanes. With their support for 40 Gigabit Ethernet (GbE) and QDR Infiniband (for board-to-board communication) and Gen3 PCI Express (for on-board data flows), these system elements enable the integration of large-scale rugged embedded subsystems that approach supercomputer processing levels. These high-end processing systems can now address challenging Intelligence, Surveillance, and Reconnaissance (ISR) applications in low- to mid-range systems with three to five boards in a small, compact chassis.

System designers can now use the latest generation of SBCs that feature dual channels of 40 Gbps bandwidth and support for 3rd Gen PCle-enabled XMC mezzanine module sites to define a new class of entry-level "HPEC-Lite" systems. With their higher 40 Gbps bandwidth, the latest SBCs can now serve as dual-use platforms in small low- to medium-level High Performance Embedded Computing (HPEC) systems, providing both their traditional system management functionality and the highspeed data ingress functionality that previously required the use of a dedicated, but lower speed, XMC I/O carrier board in an ISR HPEC system.

Small HPEC systems such as the Curtiss-Wright 6U VPX6-1958 board bring in analog front-end data to the board via its high-speed I/O XMC mezzanine cards at PCI Express (PCIe) rates (see Figure 1). The raw captured data is then sent directly from the SBC at 40 Gbps rates to one or more DSP engines for ISR application processing. This "HPEC-Lite" approach eliminates

Figure 1 | Curtiss-Wright's VPX6-1958 board, which uses the latest Intel 4th Generation Core i7 processor and dual XMC sites, enable HPEC-Lite systems for SWaP constrained ISR applications.

the need for a slower, PCIe-based XMC carrier card and the dedicated board slot it would require. Instead, the SBC functions as a high-speed intelligent router that can run a TCP/IP stack to support a redundant 40 GbE data pipe to the system's DSP engines. Via its dual/quad 40 Gbps pipes, Core i7 CPU, and high-speed XMC sites, the SBC becomes a high-end sensor I/O distribution subsystem.

The SBC's Intel 4th Generation Core Haswell processor, with its built-in GPU, can deliver unprecedented levels of performance – 300 GFLOPS from either the CPU or GPU, which combined brings more than 600 GFLOPS of performance from a single Intel processor. In an HPEC-Lite system like the one mentioned above – with a lone VPX6-1958 SBC and two DSP engines, the result is >2 TFLOPS of processing performance. This performance is expected to increase, as future Intel processors are anticipated to enable 4 TFLOPS in a similar 3-board small HPEC system.

Many ISR applications will continue to require larger board sets. However, the compact HPEC-Lite approach will enable many types of ISR applications with low Size, Weight, Power, and Cost (SWaP-C) requirements, to be solved with a small deployed chassis. For example, a radar-processing system can be built using the smaller system to bring in raw data at the front-end via Serial FPDP (sFPDP) via the SBC's XMC cards, and then transfer that raw radar

data with minimal latency to one of the system's two DSPs for post processing.

Another potential application is visualization data processing, particularly when pattern matching is required in unmanned aerial vehicles, ground combat vehicles, and airborne sensor pods. In this type of application the SBC's XMCs would use the XF05 camera link digital video-transmission standard to bring the raw video data to the small HPEC system, which would then route the data to the system's DSP engines for post processing.

In this dual-use approach, the SBC is still able to provide the traditional "traffic cop" system management functionality, but now also acts as the ingress system for the front-end data, sending raw data via PCIe to dedicated GPGPUs, or via 40 Gbps fabrics to DSP engines. For those ISR applications that require the greatest processing power and performance possible, 40 Gbps end-to-end system elements enable the development of large "big iron" scalable HPEC systems that can move terabytes of data. Yet, these high bandwidth board elements also enable designers to address less demanding applications with lowto mid-level subsets of those solutions, saving space, weight, power, and cost.

Alan Baldus

Product Marketing Manager, Intel SBCs

Curtiss-Wright Controls

Defense Solutions

www.cwcdefense.com

# DEFENSE TECH WIRE

NEWS | TRENDS | DOD SPENDS | CONTRACTS | TECHNOLOGY UPDATES

By Amanda Harvey, Assistant Editor

NEWS

# Rocket-based weapon system demonstrated for small ship protection

Engineers at Raytheon and L-3 Communications fired Raytheon-made TALON laser-guided rockets from a L-3 remote weapon station (designed by L-3) using an LAU-68 launcher. The test demonstrated how small ships can be protected by using the lightweight remote weapon system integrating the already-fielded launcher and sensor systems as well as the TALON missiles.

The system, which can carry as many as seven TALONs uses an electro-optical sensor and laser designator, for a total weight of about 500 pounds. It only needs a target queue for engaging on-mount target tracking and can be used on ships ranging in size from riverine to a major surface combatant. TALON is a cooperative development program between Raytheon and the United Arab Emirates.

Figure 1 | The Raytheon TALON laser-guided rocket were fired from a L-3 remote weapon station using an LAU-68 launcher. Photo courtesy of Raytheon.

# Frost & Sullivan predicts U.S. DoD Special Operations Command spending to stabilize through 2018

Analysis from Frost & Sullivan's U.S. Department of Defense (DoD) Special Operations Command (SOCOM) budget shows \$10.09 million was spent on military products and services in 2012, and is expected to reach \$10.60 million by 2018. The spending is anticipated to remain stable during the next four years, in spite of current budget concerns.

Frost & Sullivan also predict investments in Commercial Off-The-Shelf (COTS) products and networking tools will rise as costs are lowered and efficiency enhancements are made. In the next four years, the U.S. DoD SOCOM is also expected to spend on new platforms, including Ground Mobility Vehicles (GMVs) and training. In terms of technology, spending will primarily focus on Size, Weight, and Power (SwaP) product improvements. Analysts also predict that command and control; communications; computers; Intelligence, Surveillance, and Reconnaissance (ISR) systems; rotary-wing applications, and training and simulation programs will increase exponentially.

# Software and hardware on Marine Corps AN/TYQ-23(V)4 command, control and communications TAOM getting upgrade from Northrop Grumman

Northrop Grumman won a U.S. Marine Corps contract to deliver post-production life-cycle support for Marine Corps AN/TYQ-23(V)4 Tactical Air Operations Module (TAOM) and related subsystems through fall 2014. Under this new contract, Northrop Grumman engineers will work to sustain and upgrade the circuit card assemblies, hardware, and software of the command and control systems that support the TAOM. Software improvements will also be made to the Multi-Radar Tracker and Data Communications Unit.

The system is a transportable command, control, and communications facility that operates in conjunction with the AN/TYQ-87(V)2 Sector Anti-Air Warfare Facility and its peripheral equipment for surveillance, threat evaluation, identification, weapons coordination, communications capabilities, and airspace management. Each TAOM contains mission-essential equipment such as computers and digital voice communications systems that are required for command and control functions.

# Top Secret NSA certification given to TacNet **Tactical Radio from Rockwell Collins**

The TacNet Tactical Radio (TTR) from Rockwell Collins in Cedar Rapids, IA, garnered final National Security Agency certification to Top Secret. The TTR enables Link 16 networked communications to new users. The small form factor radio has a selectable power output with 1-, 50-, and 90-watt transmission modes; increased range; and free air convection cooling allowing it to adapt to any warfare environment. TTR provides a common operating picture through Link 16 networked communications.

Applications for TTR include unmanned aerial vehicles, rotarywing aircraft, military vehicles, forward air controllers, and mobile and transportable ground stations as well as small

maritime assets that have not had access to Link 16 capability in the past. Link 16 also integrates command and control data including the sharing of targeting and situational awareness data among joint and coalition partners. TTR has a volume of less than 185 cubic inches and weighs less than 10 pounds. For more information, visit www.rockwellcollins.com/ttr.

Figure 2 | The TacNet Tactical Radio (TTR) from Rockwell Collins received Top Secret NSA certification. Photo courtesy of Rockwell Collins.

INNOVATION | MARKET PULSE | WHITE PAPER | BLOG | VIDEO | SOCIAL MEDIA | E-CAST

# WHITE PAPER

# Thermal management challenges and solutions for avionics systems

By: Mentor Graphics Corporation

The main source of heat in electronic equipment is their semiconductor chips, and the temperature sensitivi-

ties of these chips presents a challenge in designing cooling mechanisms. Overheating causes the chips to prematurely fail, and failure of only one chip can disable the entire equipment. The higher the chip temperature, the earlier and more certain the failure. As functionality has increased, the associated heat dissipation has escalated to the extent that it is recognized as a potential limitation on the pace of electronics development. Appropriate cooling strategies are needed to prevent overheating and failure of critical components. This white paper addresses thermal design challenges for electronic products.

Read the white paper: http://opsy.st/1e3Y9Ec

More white papers: whitepapers.opensystemsmedia.com

# E-CAST

# **Enabling open architectures in rugged ISR:** Innovation in radar and electronic warfare systems through signal processing

Presented by: GE Intelligent Platforms, Mercury Systems, Pentek, and Thermacore

Gaining the tactical edge on the battlefield is becoming less about troop and tank deployments but more about who has the smartest sensors, best Electronic Warfare (EW) techniques, and the most accurate radar systems.

As the U.S. defense budget shrinks and the military reduces its global footprint, funding for these applications remains steady, even increasing in some programs. According to Frost & Sullivan radar contracts increased from a value of \$3.27 billion in 2011 to \$4.26 billion in 2012. The increased demand also places more pressure on system performance, driving innovation at the signal processing level so radar and EW systems can track every target and every signal. Often this performance is found in commercially developed, embedded signal processing components in open architecture designs. This webcast of industry experts will discuss how EW and radar system designs leverage these components and overcome challenges such as reduced Size, Weight, and Power (SWaP) requirements.

Register for the free e-cast:

http://ecast.opensystemsmedia.com/445

View archived e-casts:

http://opensystemsmedia.com/events/e-cast/archive

## E-CAST

# Maximizing system performance in time and space partitioned DO-178 certifiable safety-critical systems

Presented by: DDC-I

ARINC 653 Part 1 (653p1) defines a standard Real-Time Operating System (RTOS) Application Executive (APEX). It provides partitioning and a relatively simple, standards-based API, which facilitate porting and reuse of 653 applications.

Priority-preemptive RTOSs offer flexible scheduling models, which allow efficient scheduling of more complex applications. However, very few of these RTOSs support guaranteed execution of tasks, also known as time partitioning.

Merging these two models into a hybrid solution offers the best of both worlds: standards-based commonality and advanced features that can yield the highest performance possible for safety-critical software operation. Industry experts from DDC-I will highlight RTOS technology that allows developers to merge these two approaches into a hybrid model, and will discuss the resulting benefits.

Register for the free e-cast here:

http://ecast.opensystemsmedia.com/447

View upcoming e-casts:

http://opensystemsmedia.com/events/e-cast/schedule

# WHITE PAPER

# **Tuning HPEC Linux clusters** for real-time determinism

By: GE Intelligent Platforms, Inc.

This paper investigates interrupt response times and message passing latencies using OpenMPI on three different versions of the Linux kernel:

one "standard" server grade, one server grade with real-time pre-empt patches applied, and one with a proprietary, realtime kernel. In order to characterize these platforms, a series of measurements were made with and without a background CPU load.

This paper will also highlight some system and Linux kernel tuning techniques that can improve determinism and affect system performance. The results are presented in a series of graphs showing histograms of interrupt response and MPI message latencies under the various workloads and tuning

Read the white paper: http://opsy.st/1klogn5

More white papers: whitepapers.opensystemsmedia.com

# **Special Report**

RADAR DESIGN TRENDS

# **New capabilities** on the way for airborne maritime surveillance radars

By Sally Cole, Senior Editor

Airborne maritime surveillance radars play a central role in the global homeland defense of more than 315,000 miles of worldwide coastline. While considered state-ofthe-art, these radars continue to evolve to meet military customers' needs for persistent surveillance, automation, and continued tracking of targets as they move from sea to land.

Maritime radars are often used in Unmanned Aerial Vehicle (UAV) platforms such as the U.S. Customs and Border Patrol's Guardian. Photo courtesy of Raytheon.

From a mission standpoint, the traditional role for airborne maritime surveillance radars was anti-surface warfare, or basically detecting small targets on the ocean surface in heavy sea states. This capability was critical during the Cold War, at a time when the US Navy needed to quickly detect small targets such as Russian periscopes.

After the Cold War, the land-sea border known as the littoral zone has emerged as an area of intense interest. Within the littoral zone, the challenge for airborne maritime surveillance involves looking at thousands of targets in the water because anything floating on the surface - including debris and trash appears as a target. This can make it challenging for radar operators and mission commanders to quickly make sense of a complex tactical picture and zero in on actual targets.

Industry leaders Telephonics Corp. (Farmingdale, NY; www.telephonics.com) and Raytheon (McKinney, TX; www.raytheon. com) are addressing the littoral zone issue and many other challenges by continuing to enhance the capabilities of their airborne maritime surveillance

# Capabilities requested by military customers

What types of capabilities are military customers requesting for airborne maritime surveillance radars today? For starters, airborne maritime surveillance radar used in a military application must be military grade and able to survive the airborne environment.

"For maritime surveillance, one of the key capabilities is the ability to detect small targets at long ranges in heavy sea states," says Joseph Battaglia, president and CEO of Telephonics Corp. "Heavy seas can obscure relatively small targets, so it's important to know how to extract the target of interest from the background sea clutter, which interferes with the ability to detect the target."

The military often needs to identify targets of interest, and Inverse Synthetic Aperture Radar (ISAR) imaging is one

of Telephonics' strengths. "Telephonics' images have been referred to as 'eyewatering,' because of their high resolution and crispness. These images can help identify a battleship from a cargo ship from a pleasure yacht. Whatever the target is, you'll see a physical image of it on the radar display, as opposed to the classic radar return, which would be a dot on the screen," Battaglia says.

Military customers also want to detect targets with an Identification Friend or Foe (IFF) capability. IFF systems are typically separate systems on a platform. "Telephonics has fully integrated the IFF function into our radar systems, which along with saving size, weight, and wiring on aircraft, actually performs better than two separate systems that are required to communicate," Battaglia says.

Yet another important capability? The Ocean Surveillance Initiative (OSI), in which the automatic identification system (AIS) works with the OSI to provide a complete operating picture of the field of regard.

Adding OSI and AIS functions to maritime surveillance radars "enables persistent surveillance and a littoral capability, providing the operator a common operating picture (COP)," Battaglia explains. "Submarines are probably the worst threat to the fleet. Some of Telephonics' radars provide a periscope detection mode and are deployed on fixed-wing aircraft, helicopter platforms, and UAVs [Unmanned Aerial Vehicles] to ensure the fleet is well protected." (See Figure 1).

As part of Raytheon's recent XMC (eXpanded Mission Capability) upgrade to its SeaVue radar, the company enhanced its radar system to automatically correlate radar and AIS tracks. "The radar presents a single track to reduce clutter on the display and provide additional information to the operator," says Brad Hopper, business development director in Raytheon's Intelligence, Surveillance, and Reconnaissance systems mission area.

Although AIS is typically on larger ships – 300 tons or more – this capability is particularly useful if a small target is being tracked in a shipping lane with lots of large ships. With the click of a button, according to Hopper, the operator is able to remove those larger targets from the display and concentrate on the target of interest.

Out of concern about hijacked ships spoofing AIS, the Raytheon radar can provide an automatic length estimation of radar-detected ships. "If you're far enough away and can't get eyes on with electro-optics, now you can check it against the length AIS is sending to protect against spoofing," Hopper says.

# Persistent surveillance's influence on radar design

Persistent surveillance is influencing the design of airborne maritime surveillance radars in several ways, in particular, automation.

"Historically an operator spent more time operating the radar than understanding what's on the surface of the ocean. A significant amount of automation was added during Raytheon's XMC upgrade to SeaVue to help out in this area," Hopper notes.

For example, if you have a critical piece of infrastructure such as a power plant or oil platform and don't want anything (such as a vessel) getting close to it, you can use SeaVue XMC software to set up an exclusion zone so the operator is automatically alerted if anything moves in or out of it. "This ability to automate the process and help the operator understand what's happening in the littoral environment is significant. Customers

Figure 1 | The AN/APS-153(V) maritime radar from Telephonics Corp. is found on the U.S. Navy's MH-60R helicopter. Photo courtesy of Telephonics.

say this capability with SeaVue XMC has reduced their operator workload by 50 percent, so now they can spend time doing the real mission and not just operating the radar," Hopper says.

Being able to do precision tracking on each one of these targets also enables persistent surveillance. "One of the problems with long-term surveillance of a certain area is that small targets of interest tend to lump together and targets that are trying to hide from you will purposely get into a fishing fleet or cross into a transit lane to avoid detection," Hopper adds. "We've added precision tracking into the SeaVue XMC to help with persistent surveillance and to ensure we maintain track on that target no matter how small it is or how it's maneuvering."

# Leveraging COTS signal-processing solutions

Are new airborne maritime surveillance radar systems leveraging Commercial-Off-The-Shelf (COTS) signal-processing solutions to meet performance requirements and enable open architecture designs? Absolutely.

# Telephonics' technology tapped for US Navy UAVs

Telephonics Corp. (Farmingdale, NY; www.telephonics.com) has differentiated itself in the airborne maritime surveillance radar market by developing a technology that uses smaller, lighter-weight transmitters, which don't require high-voltage power supplies.

"Since the late 1950s, Telephonics has focused on extracting targets from background sea clutter. Our front-end designs, waveforms, algorithms, signal processing, and software are optimized for maritime surveillance," explains Joseph Battaglia, president and CEO of Telephonics.

Telephonics' RDR 1700B, or AN/ZPY-4, has no real competitor for a radar of its size, weight, performance, and price, according to Battaglia. "We believe it's unique in the world, and its application to rotary or fixed-wing platforms – including UAVs – is ideal. Weighing in at 68 pounds, its imaging, integrated AIS and OSI, and small-target detection performance at operational ranges is unique in the industry," he says.

Telephonics is providing the radar for Northrop Grumman's (Falls Church, VA; www.northropgrumman.com) MQ-8B Fire Scout, a rotary-wing UAV, which will be deployed soon.

"As far as signal processing is concerned, there are many COTS solutions you can buy off the shelf," Battaglia says. "High-speed, high-throughput processors are used to accomplish the system performance we desire. The key to achieving the requisite performance is primarily driven by the algorithms and software embedded on these processors. Telephonics' algorithms are optimized to differentiate between sea clutter and targets."

Raytheon also takes advantage of high technology in the commercial world whenever it can for its radar products. "Some of Raytheon's airborne maritime radars use COTS products, such as the Freescale PowerPC G4," Hopper says. "In this case, these are put onto a ruggedized board by a supplier like Mercury Systems, and then we buy the board. We use this kind of processor because as they improve, we want to be able to upgrade without major impact to customers."

However, "you should use care when selecting COTS components for this application because they need to be able to survive the fairly severe environment of an airborne platform," Hopper cautions.

## New capabilities on the way

Expect the trend toward reducing size, weight, and power consumption for airborne maritime surveillance radars to continue, but also watch for other interesting capabilities to emerge within the next few years.

Raytheon is currently is adding a ground-moving target indicator (GMTI) capability, based on demand from international customers. For homeland security missions, for example, if you're tracking someone bringing illegal drugs in on a vessel, you can track them right up the coastline, but then they can transfer cargo to a truck and just drive away - the maritime mode can't continue to track them. "GMTI mode will enable continued tracking, so you'll be able to get land forces vectored there to intercept them," Hopper says. "Raytheon will demonstrate GTMI capabilities for SeaVue XMC during 2014."

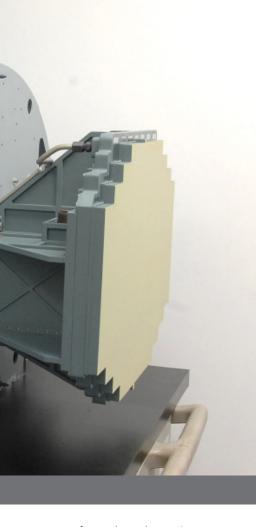

Active Electronic Scanned Array (AESA) radars using conformal antennae offer next-generation capabilities for maritime surveillance. Rather than using a rotating antenna, there are a number of ways to implement AESA radar onto a platform - in the nose of the craft, under the belly, or incorporated into the aircraft's skin as a panel.

"AESA designs eliminate moving parts, increase reliability, and offer 'graceful degradation' of a system when failures occur," Battaglia notes.

It may be a while, however, before AESA technology is ready to compete in the airborne maritime radar market with other systems for the same size, weight, performance, and price point. Highperformance AESA systems tend to be significantly larger and can be liquid cooled, which makes them bulky and expensive - but this is all likely to change at some point in the future.

# SynCor

# **Uninterruptible Power Supply**

Smaller

Lighter

More Powerful

- Power: 1250W/1500VA

- **▶** Weather-proof, shock-proof construction

- True on-line double conversion

- ▶ 1U high rack mount (17" x 22" x 1.73")

- ► Low weight 32 pounds

- Dual input (AC and DC)

- ► Battery run time >10 minutes

- Removable battery pack

- Full power operation: -20°C to +55°C

Made in the United States of America.

1-978-849-0600 www.SynQor.com

# **Special Report**

RADAR DESIGN TRENDS

# ISR as a Service: **Providing users** with affordable surveillance and reconnaissance

By Robert Smith

As the type and number of military and national security threats increase, so does the sophistication and capabilities of Intelligence, Surveillance, and Reconnaissance (ISR) systems needed to address those threats. The problem, however, is that developing and operating advanced ISR systems is costly, and in many cases a user does not have the time, resources, acquisition processes, or technological maturity to make an ISR procurement practical.

Lockheed Martin designed its Airborne Multi-INT Laboratory (AML) with an open architecture so that a myriad of intelligence-sensor combinations can be easily integrated and interchanged into the aircraft's mission system.

One of the many challenging realities of today's evolving landscape of threats is that nations, alliances, and organizations with great need for sophisticated ISR capabilities often find it difficult to develop, field, and operate those capabilities. Perhaps they lack the budget resources to procure an ISR platform or have no acquisition group available to efficiently procure such a sophisticated system. They may not have a mature ISR organization to operate the collection system, or the luxury of time to wait for the implementation of a system. For these entities, the answer lies in ISR as a Service, or ISRaaS. By procuring the specific capabilities it needs to fulfill specific mission objectives - whether they are military, homeland defense, or even disaster relief and humanitarian assistance - this type of customer can rapidly fill the gaps in its ISR capabilities according to its situational requirements.

This approach to solving a user's ISR limitations brings its own set of challenges. Because of the high variability of each user's circumstances, each solution must be customized and configured to align with a unique combination of a user's resources, organizational maturity, mission requirements, and potential export restrictions. This need for customization might, in theory, appear to undermine one of the fundamental benefits of the service model, which is the cost effectiveness realized from standardization and reuse. In practice, however, the challenges can be overcome through a modular hardware and software architecture that supports highly adaptable technology solutions combined with technical and operational expertise.

# Defining the ISR user's need and solution

The first phase in a successful ISRaaS implementation is fully defining and understanding the ISR user's problem set. This approach has some of the characteristics of a commodity, in that it seeks to offer highly capable yet cost-effective solutions by applying standardized components to a task or set of tasks. Other features, however, are more characteristic of a development program, in that the components often require a high degree of customization and, therefore, close attention to mission definition and systems integration.

It is imperative that an ISRaaS provider focuses on helping each user determine the precise nature of the capabilities that address the mission, fit their available budget, and satisfy their overall

Modern system design, which collects metadata associated with all aspects of the system, is a great advantage, as compliant metadata formats are required to facilitate content discovery queries.

ISR goals. Take, for example, a NATO member with a need for expeditionary ISR capabilities. This user has an existing ISR infrastructure and skilled operators and analysts, but its procurement budget is insufficient to acquire a new platform. In this case, they may be best served by a service-oriented solution that provides a multi-intelligence, contractor-owned airborne ISR platform and ground processing systems. The aircraft is piloted by the contractor, but the onboard mission system, ground system, and data are controlled entirely by the ISR user. If and when they are ready to purchase the capability, the user's operational experience will have greatly influenced the final requirement set, and thus reduced any procurement risks.

On the other end of the scale, in the simplest form of ISRaaS, a user may go with a contractor-owned, contractoroperated capability where the data gathered by airborne sensors – perhaps small aircraft or even an aerostat - is passed directly to the user via live data feeds and may be recorded for later processing. With the contractor in full control of sensor cueing and data gathering, this arrangement relies on close communication to identify the user's collection requirements.

In a third category, the ISR user may have a need for advanced ISR capabilities and a willingness to purchase a platform, but no desire to develop an infrastructure of analysts and processing capabilities. In this case, they may choose an ISRaaS

Figure 1 | In Lockheed Martin's palletized Dragon Shield configuration - for users who need to perform multiple missions such as airlift and ISR - the ISR sensor and processing systems are built onto pallets or trailer-like containers that can be rolled on and off aircraft.

solution that covers only the processing, exploitation, and dissemination portion of the ISR capability.

ISRaaS platforms can come in all shapes and sizes to fit user needs. Maintaining synergies with existing sovereign assets can eliminate infrastructure changes; evaluating a new philosophy by changing asset type (such as an aerostat) can help develop techniques and training for a potential future procurement; and utilizing a roll-on, roll-off containerized ISR suite carried by an existing multipurpose airlifter - as seen in Lockheed Martin's Dragon Shield in Figure 1 – can enhance the value of an existing platform and avoid the cost of an additional aircraft.

# Interfacing with a user's C2 and ISR enterprise

When the problem set and best-value solution are determined, the next challenge is implementing the interfaces and data-format compliance between the ISR system and the customer's network or networks. Nations, alliances, and organizations are understandably protective of their data-network security, yet ingesting ISR data requires exposing a number of interfaces to those networks. The first steps to making that happen include designing the ISRaaS-enabled architecture with a minimum of unique interfaces, and ensuring standardization of the data that will be transferred across those controlled interfaces.

Applying the appropriate data adapters requires very little development in most cases, especially for systems that are fully compliant with published standards. Adding to the challenge, however, can be the many available types of sensors, data streams, and customer processing systems. Depending on the user, the data feeds may include standard- and high-definition video, still images, signals intelligence (SIGINT), and others. Data may be collected from a number of sources, including electro-optical and infrared imagery, synthetic aperture radar, and Moving Target Indicators (MTI) for ground, air, maritime, and dismounted targets.

All of the various sensor outputs can be recorded as well as streamed from the platform to the ground system through a data link. Additionally, if sensor outputs are to be ingested by the end-user for further exploitation, they must be adapted to ensure compatibility in that environment. This could be as straightforward as providing standard-definition video to which a desktop user can subscribe and display in a browser, or it could take more complex forms if the data from all intelligence domains is to be ingested and processed.

Modern system design, which collects metadata associated with all aspects of the system, is a great advantage, as compliant metadata formats are

required to facilitate content discovery queries. A sophisticated ISRaaS solution enables operators, whether they're sitting in a mobile ground station or in an aircraft, to perform federated queries across metadata catalogs for all intelligence domains and locations. Recent developments are greatly improving the ease with which varied intelligence products can be integrated, queried, and displayed.

Another consideration is the sharing of data with coalition forces. NATO members, for example, adhere to a range of standardization agreements that define the way video and metadata is encoded over a network. Properly encoded data can be shared through a coalition shared database. An ISRaaS user could, for instance, capture still imagery from a streaming feed and post it for coalition partners using NATO Secondary Imagery Format without additional processing. NATO customers are then able to engage in a higher level of data sharing and interoperability with systems that participate in NATO's Joint ISR planning and operations as demonstrated in Unified Vision exercises. It is critical to remember, however, that when the platform is integrated with national, coalition, or alliance elements, designing how data flows throughout the system is a key early task.

# Future of ISRaaS

Clearly, the need for ISR capabilities continues to grow around the world as entities of all kinds seek to protect their borders, assets, and population. When acquisition cost, timeline, or technical expertise is a limiting factor for a user, ISRaaS is often a viable alternative. It enables the rapid deployment of intelligence capabilities, using a range of deployment models tailored to each user's circumstances, providing superior value for money and critical operational effectiveness for them.

Lockheed Martin is providing ISRaaS systems to a number of users via its "Dragon" family of ISR configurations that are used for various missions. The Dragon Dome, as seen in Figure 2, links ISR, air operations, and missile defense;

Figure 2 | Dragon Dome links ISR, air operations, and missile defense systems at the battle-management level, enabling users to work together in a shared environment to optimize defense operations.

Figure 3 | A flying laboratory, the AML – also known as Dragon Star – is a used business jet that Lockheed Martin engineers modified into a flying test bed for testing and fielding C4ISR capabilities. The Dragon Star configuration addresses requirements for midrange, multi-intelligence platforms such as the Gulfstream III, Havilland D-8, or Beechcraft B350, all of which can be equipped with a variety of sensor and communications systems.

while the Dragon Star flying laboratory (see Figure 3) serves as an airborne test bed for C4ISR capabilities. **MES**

Robert Smith is vice president of C4ISR Systems for Lockheed Martin Information Systems & Global Solutions. He leads a comprehensive portfolio of Command, Control, Communications, Computers, Intelligence, Surveillance, and Reconnaissance (C4ISR) programs. In this capacity, he is responsible for more than 100 programs that provide services and capabilities for all branches of the U.S. military, various national

agencies, and numerous international customers. Smith received a bachelor's degree in chemical engineering from the University of Maryland, a master's degree in business administration from Johns Hopkins University, and a doctoral degree in chemical engineering from Auburn University.

Lockheed Martin Information Systems & Global Solutions 301-897-6230 • www.lmco.com

# DRAGON it's not a myth.

- Rugged PC/104 enclosure

- Data acquisition

- MonitoringRecording

- MIL-STD-1553/1760

- AS5652 (MMSI)

H009

- ARINC-429/575

ARINC-708

- CANBusA/DD/A

- Serial Discrete

- User configurable

- COTS Expandable

- Extreme environments

- Accepts third party cards

# Mil Tech Trends

SIGNAL PROCESSING TRENDS IN RADAR, SONAR, AND ELECTRONIC WARFARE

# Embedded signal processing enables advanced radars and EW systems with low latency

By John McHale

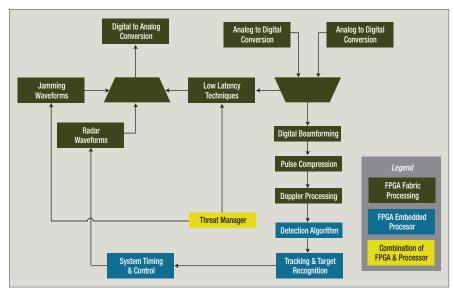

Modern radar and electronic warfare designs rely heavily on embedded computing systems that leverage high-speed commercial processors and FPGAs to find every target or signal and enable the warfighter to respond in real time. Meanwhile, signal processing system designers are cutting costs by using parallel compute platforms such as OpenCL that work across multiple chip platforms.

The basic premise of Moore's Law – that the performance and speed of integrated circuits doubles about every six months to two years - mirrors the computational demands of modern radar and Electronic Warfare (EW) systems that have ever-increasing performance requirements. Radar programs need to track sophisticated missiles and find targets in high-noise environments, while EW system designers are pressured to track all signals while remaining undetected by a sophisticated enemy. Clever algorithms drive these EW and radar platforms, but they need the right mix of commercial GPUs, multicore processors, and FPGAs to perform wonders at the sensor level.

Rugged embedded computing systems that leverage these components in low Size, Weight, and Power (SWaP) solutions enable this innovation throughout the sensor chain. Just as military program managers strive to improve the kill chain in modern weapon systems by shortening the time from sensor to shooter, radar and EW designers are

similarly looking to tighten integration along different parts of the Intelligence, Surveillance, and Reconnaissance (ISR) sensor chain to improve not only precision in data acquisition but also to deal with latency challenges. Engineers at Mercury Systems in Chelmsford, Mass., say the chain consists of six parts – acquisition, digitization, processing, storing, exploiting, and dissemination through electronic countermeasures.

"Where I see the greatest levels of integration effort is in the sensor chain, where you couple RF stages with mixed signal acquisition and digital processing stages," says Marc Couture, Director of Product Management at Mercury Systems. "The sensor chain stages are all about capturing the real world with an aperture, zooming in a target window in the electromagnetic spectrum, and presenting as much fidelity as possible to an analog-to-digital converter. This is how you know that your digital representation of the real world is as accurate as possible. Then your compute elements can go to work on the 1s and 0s."

"We can expect advances in electronics to enable tighter integration of current EW subsystem components," says Dr. Paul Monticiollo, CTO of Mercury Systems. "For example, as opposed to having separate 'boxes' for receivers, digital RF memory, signal processors, and threat managers, we expect to see a consolidation trend that will not only yield improved performance but also reduced long-term maintenance costs."

Demand is constant for more speed and more density and array type products, to process all the data being acquired, says Jenny Donaldson, President of Annapolis Microsystems in Annapolis, Md. Program managers are looking toward embedded Commercial-Off-The-Shelf (COTS) systems such as OpenVPX radar, airborne telemetry, synthetic aperture radar, and signals intelligence – anything that needs fast processing, Donaldson says. Annapolis offers the WILD OpenVPX EcoSystem that mixes and matches FPGA-based COTS OpenVPX boards.

# Improving latency

"In EW systems minimizing latency is very important," Mercury's Monticiollo continues. "Missiles move extremely fast and there is not a lot of time to react and apply a countermeasure. Systems will have to be able to operate more autonomously in case communication links are jammed. For that you will need the signal processing to have a tighter degree of interaction with the mission computer communicating between different functions and maybe even having the mission computer integrated with signal processor. Advances in SOC designs will help this and once we have these new capabilities in the circuit world we can think about how to design new systems."

"Low latency will be enabled by increased fabric speeds underneath individual boards and processors," says David Jedynak, CTO at Curtiss-Wright Controls Defense Solutions in Ashburn, Va. "The low latency requirements are pushing the move toward fabrics such as Infiniband or 40 Gigabit Ethernet, so you can move data without a lot of processor overhead. Curtiss-Wright is involved in the 40 Gigabit Initiative to provide 40 gigabits per second performance in systems from end to end."

"The biggest thing that's made a difference for us was the introduction of GPUDirect, which solved one of the challenges in using GPGPUs regarding latency in sensor data," says Peter Thompson at GE Intelligent Platforms in Huntsville, Ala. "Previously you'd take a signal across PCI Express to the Intel processor to memory and then send it to the GPU, which takes extra time and creates extra latency. With some EW applications those extra nanoseconds make a world of difference because you have a finite time to gather the signal and react. GPUDirect is a piece of technology that enables you to send sensor data straight across PCle directly to the GPU." GE offers the XVR16 6U VME rugged single board computer for signal processing applications. (See Figure 1).

## Fast FPGAs on front end

Reducing latency is also enabled by modern FPGAs on the front end of designs, where they process algorithms at very high rates. "FPGAs are front and center as the first signal processing

element for our radar customers," says Rodger Hosking, Vice President and co-founder of Pentek in Upper Saddle River, N.J. "What they are doing with radar is trying to enhance detection range, bring more resolution to the front end, etc. This all ties into getting higher resolution on the de-converters, which ties into the ability to achieve higher precision with the radar detection algorithms, so they can detect smaller targets that have weaker signal levels. They want to track the targets that are buried in noise with these algorithms and the de-converters can pull those signals out. Another thing FPGA

Figure 1 | GE's XVR16 6U VME rugged single board computer uses the Haswell 4th generation Corei7 processor from Intel.

technology enables is target classification and identification by helping correlate vehicle signatures with a known database of targets - figuring out who to whom each signal belongs."

# Smart Ethernet & Avionics Protocol Converter...

AceXtreme® Bridge Device

Enables Ethernet based system upgrades on 1553/429 data bus networks...

- Onboard processor provides programming flexibility and automatically bridges messages in real-time between Ethernet, ARINC-429, and MIL-STD-1553 in any direction, without a host computer.

- · Turnkey software for seamless integration.

Enables remote access via Ethernet to 1553/429 connections.

"There is innovation coming with the next generation of FPGAs," Monticiollo says. "They are extremely more powerful with microprocessors being built in and heading toward true System-on-Chip (SoC) designs. High-performance FPGAs, microprocessors, and multicore processors can all be integrated on the same die, which will reduce latencies to microseconds and even nanoseconds for some applications."

"FPGAs are good at processing wideband radar signals in real time," Hosking says. "They are better than generalpurpose processors (GPPs) They are better than GPPs in this instance because of the data rate. For example, radar systems can have as many as 48 lines running at 900 megahertz each and the only animal that can that is an FPGA. They enable flexibility in the mechanical arrangement of things throughout a radar system - not just with signal processing. For example I could also choose to put the sensor up on a box on an antenna then do the digitization and send it across the fiber optic link at high speeds to an FPGA. "Pentek's latest FMC carrier board for radar applications has an optical backplane interface. The 3U VPX product - the Model 5973 - is the first one from of their new Flexor line of FMC (FPGA Mezzanine Card) carriers and FMC modules.

Some industry experts see generalpurpose processors taking over more of the DSP functions of FPGAs, leaving them to focus on the RF side, while reducing the costs and time associated with programming FPGAs.

"Within signal-processing applications such as radar, there is a trend to do more of the DSP functions handled by FPGAs on a GPP," says Glenn Johnson, at Kontron in Poway, Calif. "This can make the design process more efficient and less costly as programming FPGAs in VHDL is still difficult and expensive. FPGAs in recent years have been able to do things that processors were never able to do. They started out on the RF end and progressed backwards to where they obsoleted DSP chips and ended up doing general processing. Now, thanks

to advances with chips like the Intel Haswell device, the GPP is taking that burden off of the FPGAs, enabling them to focus on the RF receive and transmit chains." Kontron's Haswell offerings include COM Express, Mini-ITX, 6U CompactPCI, and SYMKLOUD products.

Haswell and military signal processing While designed more with the gaming industry in mind, Intel's 4th generation Core i7 iteration, originally codenamed Haswell, has military signal-processing designers as excited as a teenager with a new Xbox on his birthday. Often working in tandem with FPGAs on a board, the device is enabling leaps in computing performance.

"Intel dramatically improved the AVX 2.0 math instructions, which on an SAR algorithm can improve performance by as much as 50 percent," says Eran Strod, Systems Architect at Curtiss-Wright Controls Defense Solutions. "Also, following the tenets of Moore's Law, the device takes up less die space and has these tiny tiny graphics execution units that provide hundreds of MFLOPS. For example our 6U CHAMP-AV9 boards with Haswell will be running at 1.2 teraflops – that's five times faster than current devices."

"Haswell will enable radar/EW system performance enhancements with functions such as pulse compression, beamforming, Doppler processing, etc.," Mercury's Couture says. "AVX 2 enables it to do the linear math and DSP necessary for radar signal processing at very high speeds. Another advantage with Haswell is on the power-management side, improving performance per SWaP at the individual core level. Essentially it will slow down certain cores that are running less taxing tasks while speeding up others performing intensive tasks. The primes like Haswell because it can attack more channels with wider bandwidth providing for more coverage in the electromagnetic spectrum at any given time."

"What's disruptive about this product is the larger bandwidth and spectrum digitization, which improves not only the radar system's ability to identify and track targets but also helps it avoid detection," says Bill Pilaud, Continuum HPEC Manager at Curtiss-Wright Controls Defense Solutions. "You protect the warfighter by sending information in one band and then switching to another instantaneously, moving the signal around faster than anyone can track it."

# Saving costs through software development

Budget cuts and sequestration have the U.S. military looking everywhere to save pennies without compromising performance. In signal-processing systems they are achieving this though modular, open architectures that can leverage existing software code across multiple platforms.

"There is a lot of pressure to cut costs and to do that the integrators are looking deeper into the supply chain for help with integration," Curtiss-Wright's Strod explains. "They are looking for more re-use of software code from platform to platform to save on what can be extremely expensive development costs. They want to be able to take one platform-development effort and leverage it into multiple platforms."

"Radar customers don't just want open architectures, but to a large degree they want modularity in the system as a whole," Thompson says. "They are looking at the entire system and breaking it up into pieces and want to have different interfaces for hardware and software to make it far easier to change individual pieces of the chain without affecting pieces to the left and right of it.

"That is starting to have an impact on what they want from embedded computing companies like GE Intelligent Platforms," he continues. "In the past we would provide the hardware implementation of a radar processor, but now we are seeing a push to provide software solutions – not the radar application, but providing a level of middleware that is maybe more tilted toward the application than with previous applications. Before Haswell, GE started combining

CPUs and GPUs on a single board with three-quarters of a teraflop in a single slot and now we have a sister product in 3U and 6U SBCs with Haswell in a VPX architecture."

The cost of software development can also be quite high when upgrading to a VPX system from a legacy VME design. Sometimes users will shy away from it because of this, "so we are helping our customers port the software," Couture says. Mercury did this with their upgrade of the Patriot Missile Defense System radar. "To be specific, Mercury didn't compose or tamper with the customers' algorithms of application code, but we did migrate the DSP libraries and the fabric infrastructure 'plumbing' right underneath their application. That brought them from 1990s technology right into the 2010s."

# Parallel compute languages

Open-standard software-development tools also are giving signal-processing system designers another way to reduce costs and development time. "When integrating systems with Haswell chips, FPGAs with ARM cores, etc., there are challenges in the upfront development process with time and expense," Couture says. However, tools such as CUDA and OpenCL enable designers to work across processing platforms, with hardware no longer a dominating cost in terms of product development. Algorithm and infrastructure development are where the most expense is incurred in signal-processing designs. The trend is for the signal-processing system vendor to help lessen that burden for the end user. With open systems such as OpenVPX, there is a greater focus on software development and managing the associated costs, which can be extreme. However, parallel compute languages such as CUDA and OpenCL enable designers to work across processing platforms to reduce these costs.

"CUDA is efficient with NVIDA GPUs and the Corefire tool from Annapolis works really well - but only with Annapolis products," Couture continues. "OpenCL, however, is the first thing I've seen that Texas Instruments, AMD, Xilinx, Altera, ARM, and Intel all support - and the list is growing." **MES**

# /ww.aviftech.com/test

# **TEST INSTRUMENTATION**

Simulation, Analysis, & Verification Reliable Databus Network Systems

- ◆ MIL-STD-1553

- ARINC 429

- ARINC 664p7

- Fibre Channel

- HS1760/MIL-STD-1760E

- ◆ AS6802 Deterministic Ethernet

Complete Test & Simulation Solutions with the Industry-leading Flight Simulyzer™ and fcXplorer™ GUI Analyzer/Simulator and AIT's Software Development Kits

# Mil Tech Trends

SIGNAL PROCESSING TRENDS IN RADAR, SONAR, AND ELECTRONIC WARFARE

# Using highperformance SRAMs to increase performance in DSP-intensive applications

By Suhail Zain

Military applications such as radar, Software Defined Radio (SDR), smart munitions and targetdetection systems, Electronic Warfare (EW), aircraft imaging, and many more benefit from Digital Signal Processors (DSPs). DSPs accelerate performance using deterministic processing and have capabilities that include real-time signal processing, extremely high throughput, and reprogrammability. However, signal processing demands for radar, EW, and other programs continue to increase so DSP system users continue to search for innovation that will boost performance. That need is being answered by use of a combination of Quad Data Rate (QDR) Static Random Access Memory (SRAM) that – at a minimum – doubles the performance of more traditional Synchronous Dynamic Random Access Memory (SDRAM).

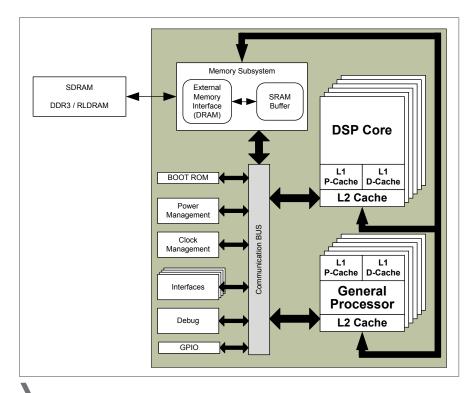

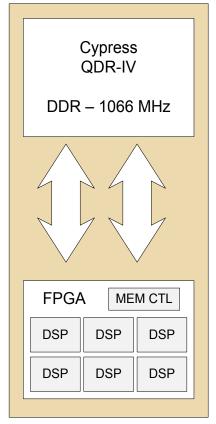

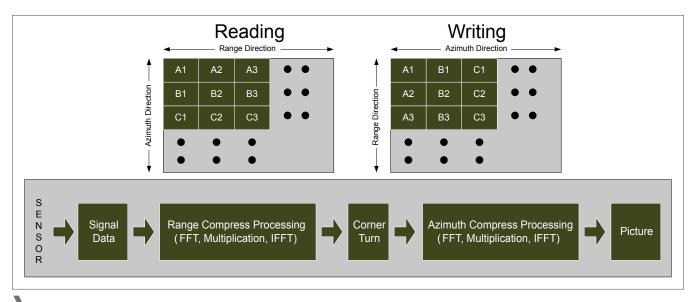

Figure 1 | TI's multicore DSP architecture.

## Digital signal processing

Digital signal processing encompasses techniques to manipulate signals after they have been converted into digital form as seen in radar processing. They are used for several functions in radar systems such as pulse compression, signal filtration, and pulse modulation. These components differ from general-purpose microprocessors in that they are designed for the types of fast mathematical calculations (multiplication and addition) most commonly used to design filters like FFT and Finite Impulse Response (FIR). Typically, FFT filters are used for domain conversion - time to frequency and vice versa - whereas FIR filters are used for signal separation and signal restoration.